Kontinuierliche Timing-Sicherstellung

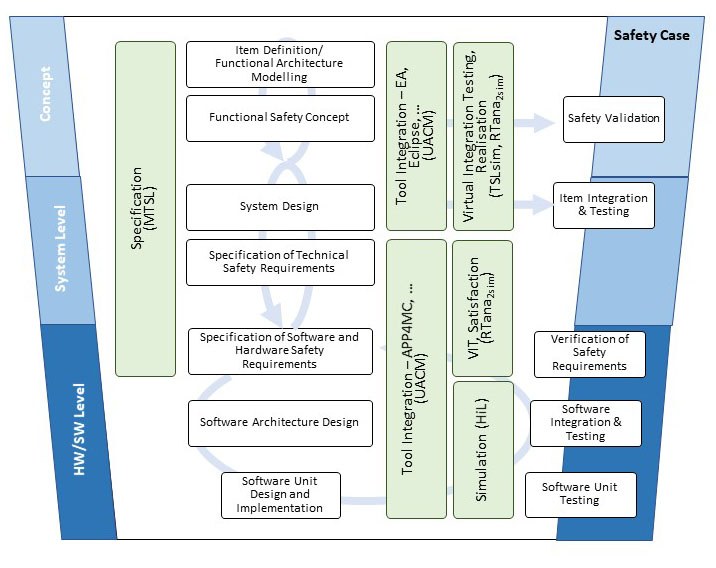

Die Sicherstellung zeitlicher Eigenschaften ist ein entscheidender Aspekt bei der Entwicklung sicherheitskritischer Systeme. So gehört zum Beispiel zum sicheren Betrieb hochautomatisierter Fahrzeuge die Fähigkeit, auf erkannte Hindernisse in einer bestimmten maximalen Zeit zu reagieren. Unser Asset „Kontinuierliche Timing-Sicherstellung“ bietet Methoden und Werkzeuge, die die Spezifikation, Verifizierung und Überwachung der zeitlichen Eigenschaften während des gesamten Systemlebenszyklus ermöglichen: Von der Spezifikation, Implementierung und Prüfung in der Entwicklungsphase bis hin zur Überwachung, Diagnose und Rückmeldung an die Entwickler in der Betriebsphase.

Das Asset bietet Fachwissen über die zugrundeliegen Entwicklungs- und Betriebsprozesse (DevOps), in denen diese Methoden und Werkzeuge angewendet werden, da sie integraler Bestandteil vieler Sicherheitsstandards sind, die in der Industrie befolgt werden müssen. Die Fähigkeit zur kontinuierlichen Timing-Sicherstellung ist für Hersteller und Lieferanten von softwaredefinierten hochautomatisierten Systemen von entscheidender Bedeutung, da sie durch regelmäßige Software-Updates und die sich wiederholenden Echtzeitnachweise besonders gefordert sind.

Kernmodule

Das Asset baut auf zwei Kernmodulen auf. Die MULTIC Timing Specification Language (MTSL) ist eine Sprache für die Spezifikation von Timing-Eigenschaften von Systemen im vertragsbasierten Entwurf. Das Unified Abstract Component Model (UACM) ist ein Zwischenformat zur Spezifikation von Komponentenmodellen, die mit MTSL-Spezifikationen für den Austausch von Systembeschreibungen zwischen verschiedenen Modellierungs- und Analysewerkzeugen annotiert sind.

Spezifikation und Entwurf

Die Ergebnisse können in industriellen Entwurfsprozessen mit Hilfe von Modelltransformationen angewendet werden, die im eigenen Haus entwickelt und in die von den Ingenieuren verwendeten industriellen Modellierungsumgebungen integriert werden können, zum Beispiel ein Adapter für Sparx Systems Enterprise Architect zur Generierung von UACM-Zwischendarstellungen aus SysML-Designmodellen. Ein Adapter für Eclipse APP4MC ermöglicht die Generierung von RTana2sim-Analysemodellen auf Basis von domänenspezifischen Hardware/Software-Modellen. In Zukunft sollen weitere Anbindungen an etablierte Entwurfswerkzeuge und do-main-spezifische Sprachen realisiert werden, um beispielsweise Robot Operating Systems (ROS) Modelle zu unterstützen.

Analyse und Diagnose

Für die Analyse von Timing-Eigenschaften zur Entwurfszeit werden verschiedene Werkzeuge entwickelt, wie der zeitdiskrete Model-Checker RTana2sim sowie die Echtzeit-Simulationsplattform TSLsim auf Basis von SystemC und Timed-Value Stream (TVS). Sie ermöglichen eine umfassende Analyse der zuvor definierten MTSL- und UACM-Spezifikationen. Die Trace-Generierung aus RTana2sim und TSLsim, zum Beispiel in den gängigen VCD- und BTF-Trace-Formaten, ermöglicht eine effiziente Visualisierung der Analyseergebnisse.

Online-Überwachung

Timing-Spezifikationen können zur Laufzeit über TVS-basierte Timing-Monitore für die parallele Post-Mortem-Trace-Analyse oder die Online-Überwachung für vernetzte Prozessoren der Anwendungsklasse (mit hoher Leistung) ausgewertet werden. UACM::Monitors bietet Monitorgenerierung für Bare-Metal-Embedded-Plattformen (im Aufbau) und dient als Basis für echtzeitfähige Online-Überwachung auf ressourcenbeschränkten Bare-Metal-Embedded-Plattformen (Systeme ohne Betriebssystem).

UACM::Monitors for ROS 2 (im Aufbau) bietet Online-Monitoring für ROS 2-basierte Systeme. UACM::Monitors for Scalexio (in Vorbereitung) lassen sich nahtlos in die dSPACE Scalexio Hardware-in-the-Loop-Prototyping-Umgebung integrieren, um In-Process-Tests zu ermöglichen.